l'Interface Électrique :

Note : Dans tout ce document, j'emploierai le terme plus général "centre serveur" pour me référer à l'ordinateur -- ou à celui auquel le clavier ou la souris sont reliés -- et le terme "périphérique" se rapportera au clavier ou à la souris.

Vcc/Ground fournissent la puissance au clavier ou à la souris. Le

clavier ou la souris ne doit pas tirer plus de 275 mA du centre serveur et on

doit veiller aux surtensions transitoires. De telles surtensions peuvent

être provoquées "en branchant à chaud" le clavier ou la souris.

En résumé: Caractéristiques de Puissance

Vcc = +4.5V à +5.5V.

Courant maximum = 275 mA.

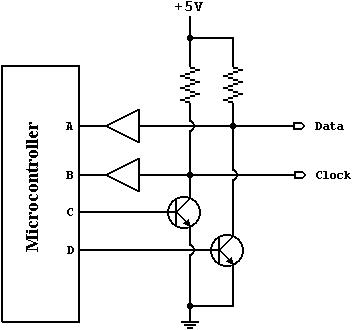

Les lignes de données et d'horloge sont toutes deux open-collector avec des

résistances de pullup à Vcc. Une interface "open-collector" a deux états

possibles : impédance basse ou élevée . Dans l'état bas, un transistor

met la ligne à la masse. Dans l'état "d'impédance élevée", l'interface

agit en tant que circuit ouvert et ne met pas la ligne en état bas ou

haut. En outre, une résistance de "pullup" à reliée à Vcc

ce qui met la ligne en état haut si le transistor n'est pas actif. La

valeur exacte de cette résistance n'est pas très importante (1 ~ 10 kOhms)

; des valeurs élevées ont comme conséquence moins de demande d'énergie

et de plus petites un temps de montée plus rapide. Une interface open-collector

générale est montrée ci-dessous :

Le schéma 1 : Interface open-collector générale. Des données et l'horloge sont lues sur les broches A et B du microcontrôleur, respectivement. Les deux lignes sont normalement maintenues à +5V, mais peuvent mises à la masse en appliquant "1" sur les broches C et D. En conséquence, A égale D inversée, B égal C inversée.

Note : En regardant les exemples de ce site Web,

vous verrez quelques trucs utilisant une interface open-collector avec les microcontrôleurs

PIC. J'utilise la même broche pour entrée et sortie, et j'utilise les

résistances internes de pullup du PIC plutôt que des résistances externes. Une

ligne est mise à la masse en plaçant la broche correspondante en sortie,

et en écrivant un "zéro" sur ce port. La ligne est placée à l'état "d'impédance

élevée" en plaçant la broche en entrée. Tenant compte des diodes

intégrées de protection du PIC et du courant de sortie suffisant, je pense que

c'est une configuration valide.

Communication :

Description Générale

La souris PS/2 et le clavier mettent en application un protocole série

synchrone bidirectionnel. Le bus est "à vide" quand les deux lignes

sont hautes (open-collector). C'est le seul état où on permet que le clavier

ou la souris commencent à transmettre des données. Le centre serveur a

le contrôle final du bus et peut empêcher la communication à tout moment en

mettant la ligne d'horloge à l'état bas.

Le périphérique produit toujours un signal d'horloge. Si

le centre serveur veut envoyer des données, il doit d'abord empêcher la communication

du périphérique par la mise à l'état bas de la ligne

d'horloge. Le centre serveur met alors la ligne de données à

l'état bas et libère l'horloge. C'est la "Demande d'Envoi" et le

signal au périphérique de générer des impulsions

d'horloge.

Toutes les données sont transmises un byte à la fois et chaque byte est envoyé sous forme d'une trame se composant de 11-12 bits. Ces bits sont:Résumé : États bus

Données = haut, horloge = haut : État à vide.

Données = haut, horloge = bas : Communication Empêchée.

Données = bas, horloge = haut : Le Centre serveur Demande-à-Envoyer

Le bit de parité est mis à 1 s'il y a un chiffre pair de 1 dans les bits d'information et à 0 s'il y a un nombre impair de 1 dans les bits d'information. Ceci est employé pour la détection des erreurs. Le périphérique doit vérifier ce bit et s'il est incorrect répondre comme s'il avait reçu une commande inadmissible.

Les données envoyées du périphérique au centre serveur sont lues sur le front descendant du signal d'horloge ; les données envoyées du centre serveur au périphérique sont lues sur le front montant . La fréquence de base doit être dans la gamme 10 - 16.7 kilohertz. Ceci signifie que le signal d'horloge doit être haut pendant 30 - 50 micro-secondes et bas pendant 30 - 50 micro-secondes. Si vous concevez un clavier, une souris, ou un émulateur de centre serveur, vous devez modifier ou échantillonner la ligne de données au milieu de chaque créneau. C.-à-d.. 15 - 25 micro-secondes après la transition appropriée d'horloge. Encore une fois, le périphérique génère toujours du signal d'horloge, mais le centre serveur a toujours le contrôle final de la communication.

La synchronisation est absolument cruciale. Chaque fois, le timing que je donne dans cet article doit être suivi exactement.Les lignes de données et d'horloge sont deux collecteurs ouverts. Une résistance est reliée entre chaque ligne et +5V, ainsi l'état "à vide" du bus est haut. Quand le clavier ou la souris veut envoyer l'information, elle doit d'abord s'assurer que la ligne d'horloge est à l'état haut. Si elle ne l'est pas, le centre serveur empêche la communication et le périphérique doit "buffériser" les données à envoyer jusqu'à ce que le centre serveur libère l'horloge. La ligne d'horloge doit être à l'état haut de façon continue pendant au moins pendant 50 micro-secondes avant que le périphérique puisse commencer à transmettre ses données.

Comme je l'ai mentionné dans la section précédente, le clavier et la souris emploient un protocole périodique avec des trames de 11 bits. Ces bits sont:

Schéma 2 : communication

de périphérique-à-centre serveur. La ligne de données

change d'état lorsque la ligne d'horloge est à l'état haut

et la donnée est valide lorsque l'horloge est à l'état

bas.

Schéma 3 : Scan Code pour la touche "Q" (15h) envoyée par un clavier à l'ordinateur. La voie A est le signal d'horloge ; La voie B est le signal de données.

---

La fréquence d'horloge est de 10-16.7 kilohertz. Le temps à partir du

front de montée d'une impulsion d'horloge à une transition de données doit être

au moins de 5 micro-secondes. Le temps d'une transition de données au

front de descente d'une impulsion d'horloge doit être au moins de 5 micro-secondes

et pas plus grande que 25 micro-secondes.

Le centre serveur peut empêcher la communication à tout moment en mettant à

l'état bas le signal d'horloge pendant au moins 100 micro-secondes. Si

une transmission est inhibée avant la 11ème impulsion d'horloge, le périphérique

doit interrompre la transmission en cours et se préparer à retransmettre

le "gros morceau" des données quand le centre serveur libère l'horloge. Un

"gros morceau" des données a pu être un Make Code, Break Code, une identification

de périphérique (ID), un paquet de mouvement de souris, etc...

Par exemple, si un clavier est interrompu lorsqu'il envoie le deuxième

byte d'un code à deux octets de Break Code, il devra retransmettre les deux

bytes de ce Break Code et pas simplement celui qui été interrompu.

Si le centre serveur met à 0 le signal d'horloge avant la première transition haut vers bas d'horloge, ou après le front descendant de la dernière impulsion d'horloge, le périphérique n'a pas besoin de retransmettre la donnée. Cependant, si de nouvelles données sont à transmettre, il faudra les "buffériser" jusqu'à ce que le centre serveur libère l'horloge. Les claviers ont pour cela un buffer de 16 bytes. Si plus de 16 bytes de frappes se produisent, elles seront ignorées jusqu'à ce qu'il y ait place dans le buffer. Les souris stockent seulement le paquet de mouvement le plus récent pour la transmission.

Communication de Centre-à-périphérique :

Le paquet est envoyé un peu différemment dans la communication de centre-à-périphérique...

Tout d'abord, le périphérique PS/2 génère toujours du signal d'horloge. Si le centre serveur veut envoyer des données, il doit d'abord mettre l'horloge et les lignes de données dans l'état "Demande-à-envoyer" comme suit :

Après que le bit d'arrêt soit reçu, le périphérique donnera accusé réception du byte reçu en mettant la ligne de données à l'état bas et en générant une dernière impulsion d'horloge. Si le centre serveur ne libère pas la ligne de données après la 11ème impulsion d'horloge, le périphérique continuera à produire des impulsions d'horloge jusqu'à ce que la la ligne de données soit libérée (le périphérique produira alors une erreur.)

Le centre serveur peut avorter la transmission avant la 11ème impulsion d'horloge (Bit d'acquiescement) en maintenant l'horloge à l'état bas pendant au moins 100 micro-secondes.

Pour rendre ce processus un peu plus facile à comprendre, voici les étapes que le centre serveur doit suivre pour envoyer des données à un périphérique PS/2 :

1) mettre la ligne d'horloge à l'état bas pendant au moins 100 micro-secondes.

2) mettre la ligne de données à l'état bas.

3) libérer la ligne d'horloge.

4) attendre que le périphérique mette la ligne d'horloge à l'état bas.

5) Set/reset la ligne de données pour envoyer le premier bit d'information

6) attendre que le périphérique mette la ligne d'horloge à l'état haut.

7) attendre que le périphérique mette la ligne d'horloge à l'état bas.

8) répéter les étapes 5-7 pour les sept autres bits d'information et le bit de parité

9) libérer la ligne de données.

10) attendre que le périphérique mette la ligne de données à l'état bas.

11) attendre que le périphérique mette la ligne d'horloge à l'état bas.

12) attendre que le périphérique libère les lignes de données et d'horloge

Le schéma 3 montre cela graphiquement et le schéma 4 sépare

la synchronisation pour montrer quels signaux sont produits par le centre serveur,

quels signaux sont produits par le périphérique PS/2. Notez

le changement de la synchronisation pour le bit "ACK" -- les transitions de

données surviennent quand la ligne d'horloge est haute (plutôt que quand elle

est basse comme c'est le cas pour les 11 autres bits.)

Schéma

3 : Communication de Centre-à-périphérique.

Le schéma 4 : Communication détaillée de centre-à-périphérique.

En référence au schéma 4, il y a deux quantités

de temps que le centre serveur recherche.

(a) est le temps que prend le périphérique

pour commencer à produire des impulsions d'horloge après que le centre serveur

ait mis initialement la ligne d'horloge à l'état bas, qui ne doit

pas être supérieure à 15 ms

(b) est le temps qu'il faut pour que le paquet

soit envoyé, qui ne doit pas être supérieur à 2 ms.

Si l'un ou l'autre de ces délais n'est pas respecté, le centre serveur

doit produire d'une erreur. Juste après que le "ACK" est reçu, le centre

serveur peut mettre la ligne d'horloge à l'état bas pour empêcher

la communication pendant qu'il traite des données. Si la commande envoyée

par le centre serveur exige une réponse, cette réponse doit être reçue pas plus

tard que 20 ms après que le centre serveur a libéré la ligne d'horloge.

Si ceci ne se produit pas, le centre serveur produit d'une erreur.